25나노 공정보다 생산성 30%↑, 소비전력은 25% ↓..30나노 D램보단 생산성 2배

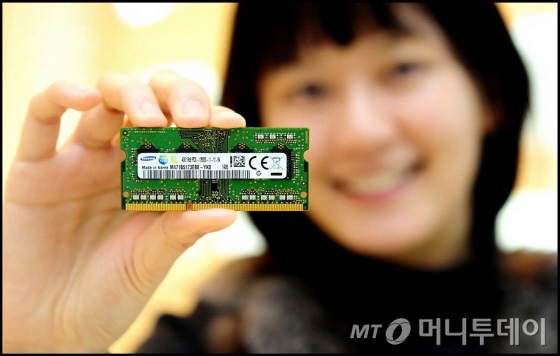

삼성전자가 이달부터 세계 최초로 차세대 '20나노(1나노 : 10억분의 1미터) 4기가비트(Giga bit) DDR3(Double Data Rate 3) D램'을 본격 양산하기 시작했다고 11일 밝혔다.

20나노 미세 회로선폭은 사람의 머리카락 두께의 2500분의 1 정도로 얇은 두께로 원자의 크기(0.2~0.3 나노미터)의 100배에 못 미치는 극미세 공정이다.

삼성전자에 따르면 20나노 D램은 2012년 삼성전자가 세계 최초로 양산한 25나노 D램보다 30% 이상, 30나노급 D램보다는 2배 이상 생산성이 높다. 20나노 공정을 적용할 경우 30나노 공정을 이용하는 것보다 웨이퍼 한장에서 생산할 수 있는 칩의 수가 2배 이상 된다는 얘기다.

삼성전자(178,400원 ▼11,200 -5.91%)는 독자기술을 통해 기존 설비만으로도 20나노 D램 미세화 기술의 한계를 돌파하고 최소형 4기가비트 D램을 본격 양산함으로써 메모리 기술의 새로운 지평을 열었다고 자평했다.

삼성전자가 이번에 양산에 성공한 20나노 D램에는 삼성전자의 신개념 '개량형 이중 포토 노광 기술'과 '초미세 유전막 형성 기술'을 동시에 적용했다.

낸드플래시는 셀(정보저장의 최소단위)이 트랜지스터 하나로 구성돼 구조가 비교적 단순하지만, D램은 셀이 트랜지스터와 캐패시터 적층구조로 구성되기 때문에 20나노 공정 미세화가 더욱 어려웠다.

삼성전자는 이러한 D램 공정한계를 독자기술인 '개량형 이중 포토 노광 기술'을 통해 극복해 기존 포토장비로도 20나노 D램은 물론 차세대 10나노급 D램도 양산할 수 있는 기반기술을 마련한 것이다.

이중포토 노광기술은 한번 패터닝한 회로 위에서 초점을 약간 이동한 후 다시 한번 노광공정을 하는 형태다. 40나노 간격을 가진 연필 두자루를 묶어서 한차례 선을 그은 후 그려진 두 선 사이에 같은 연필을 갖다 대고 한번 더 선을 그어서 회로 선의 간격을 20나노로 좁히는 형태로 이해할 수 있다.

또한 셀 캐패시터의 유전막을 형성하는 물질을 기존 나노단위에서 옹스트롬(10분의 1나노) 단위로 초미세 제어함으로써 균일한 유전막을 만들어 20나노에서도 우수한 셀 특성을 확보했다.

독자들의 PICK!

그동안은 분자구조의 유전막을 이용해 전하를 캐파시터에 채웠으나, 회로공정이 미세해지고 유전막이 얇아져 전류가 누설돼 제대로 반도체의 특성을 잡지 못했으나, 유전막을 더 촘촘한 원자구조의 물질로 바꿔 전류누설을 막아 문제를 해결했다는 게 삼성전자의 설명이다.

20나노 DDR3 D램 모듈은 PC에서 기존 25나노 대비 소비전력을 25% 절감할 수 있어 글로벌 IT 업체들에게 최고 수준의 '초절전 그린 IT 솔루션'을 제공한다.

전영현 삼성전자 메모리사업부 전략마케팅팀장(부사장)은 "저전력 20나노 D램은 PC 시장에서 모바일 시장까지 빠르게 비중을 확대하며 시장의 주력 제품이 될 것"이라며, "향후에도 차세대 대용량 D램과 그린메모리 솔루션을 출시해 글로벌 고객과 함께 세계 IT 시장 성장에 크게 기여할 것"이라고 밝혔다.

앞으로도 삼성전자는 10나노급 차세대 D램 제품을 선행 개발함으로써 반도체 기술의 한계를 극복하고 메모리 시장의 성장세를 지속적으로 주도할 계획이다.

한편 시장 조사기관 가트너에 따르면 세계 D램 메모리 시장은 올해 379억달러로 지난해 356억달러보다 6.5% 성장할 것으로 전망된다.